MIPS is a simple, efficient processor architecture that uses a basic set of instructions designed for quick execution and easy pipelining. It focuses on speed and simplicity, making it ideal for tasks in embedded systems or academic settings. However, it doesn’t support advanced features like out-of-order or speculative execution, which more complex designs offer. If you want to understand how MIPS achieves high efficiency and where it’s limited, there’s more to explore.

Key Takeaways

- MIPS is a simple, RISC-based instruction set designed for fast, efficient processing through a streamlined, uniform instruction format.

- It excels at executing instructions quickly using pipelining, which overlaps instruction stages for higher throughput.

- MIPS focuses on simplicity and predictability, lacking advanced features like out-of-order or speculative execution found in more complex architectures.

- It does not support extensive instruction sets or complex software directly, making it ideal for embedded systems and academic use.

- Overall, MIPS emphasizes efficiency and speed over versatility or support for complex computing tasks.

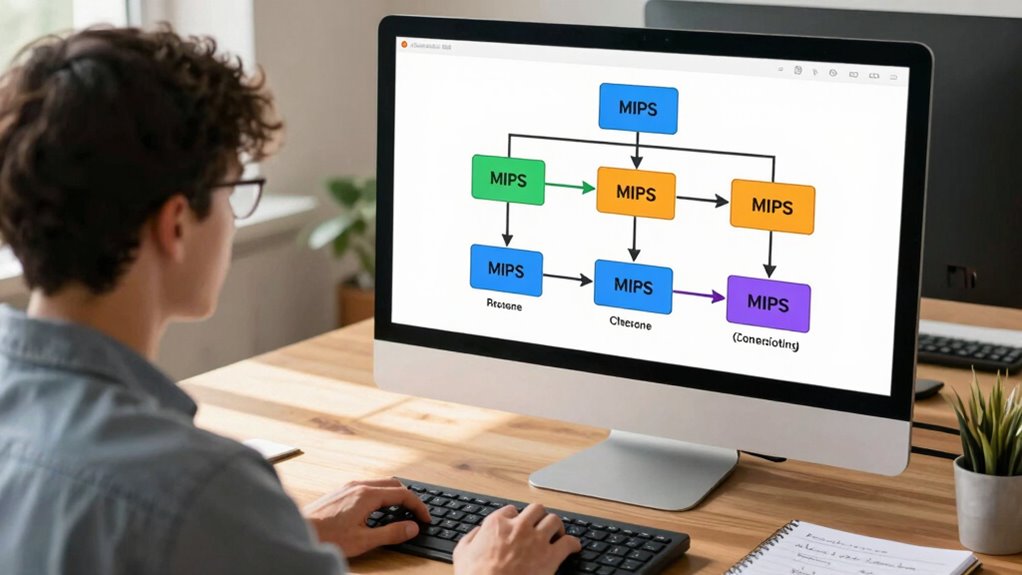

Have you ever wondered how computer processors perform millions of instructions per second? It all comes down to how they handle and execute instructions efficiently. At the core of this process is the instruction set, which is a predefined collection of commands that the processor understands and can execute directly. Think of the instruction set as the processor’s vocabulary—each instruction tells the processor to perform a specific task, like adding numbers or moving data from one place to another. The way these instructions are processed is critical for speed and efficiency, and that’s where the instruction pipeline comes into play. An instruction pipeline allows the processor to work on multiple instructions simultaneously by breaking down the execution process into stages. Instead of waiting for one instruction to complete before starting the next, the pipeline overlaps these stages, much like an assembly line, so multiple instructions are in different phases of execution at once. This technique markedly speeds up processing because it keeps the processor busy, reducing idle time and maximizing throughput.

In the context of MIPS, a simplified yet powerful RISC (Reduced Instruction Set Computing) architecture, the instruction set is designed to be straightforward and easy to decode, which makes pipelining more efficient. MIPS instructions are uniform in length, typically 32 bits, and follow a consistent format, which simplifies the process of breaking down instructions into pipeline stages like fetch, decode, execute, memory access, and write-back. Because of this regularity, the instruction pipeline can operate smoothly without complex control logic needed for variable-length instructions. This simplicity enables MIPS processors to achieve high clock speeds and maintain consistent performance, especially in applications where predictable and fast execution is essential.

However, it’s important to understand what MIPS does and doesn’t do. MIPS is primarily focused on executing instructions quickly using pipelining, but it doesn’t handle complex tasks like advanced out-of-order execution or speculative execution found in some more advanced architectures. It also doesn’t include an extensive instruction set like x86 processors, which means it’s less suited for running complex software directly but excels in embedded systems, academic environments, and situations where efficiency and simplicity matter most. While MIPS can be scaled with extensions, its core strength remains in its straightforward instruction set and efficient pipeline design, making it a clear example of how careful architecture choices can lead to high-speed processing with minimal complexity.

Keter 150 Gallon Resin Large Deck Box Organization and Storage Box for Patio, Outdoor Cushions, Garden Tools, Brown

LARGE OUTDOOR STORAGE BOX: Fashionably store your outdoor furniture cushions, pool floats, and more. This outdoor storage bench...

As an affiliate, we earn on qualifying purchases.

Frequently Asked Questions

How Does MIPS Compare to Other CPU Architectures?

You’ll find that MIPS has a simpler instruction set compared to architectures like x86, making it easier to learn and optimize. While it offers good performance, it’s less compatible with mainstream software due to its compatibility standards. In contrast, architectures like ARM and x86 dominate the market, but MIPS excels in embedded systems and academic settings because of its streamlined design. Overall, it’s a trade-off between simplicity and widespread compatibility.

Can MIPS Be Used in Modern Smartphones?

You might be surprised, but MIPS isn’t commonly used in modern smartphones. While it offers efficient performance, most manufacturers prefer ARM for smartphone integration due to its widespread compatibility and advanced features. MIPS chips struggle with modern compatibility requirements, making them less suitable for current smartphone technology. That said, if you’re exploring specialized or legacy devices, MIPS could still find a niche, but for everyday smartphones, ARM dominates.

What Industries Primarily Use MIPS Technology?

You’ll find MIPS technology primarily in industries like embedded systems and academic research. Companies use it for designing efficient, low-power processors in devices such as routers, set-top boxes, and printers. Academic institutions also utilize MIPS for research and teaching in computer architecture due to its simplicity and open architecture. Its versatility makes it ideal for applications requiring reliable performance and customization in embedded environments.

Are There Open-Source MIPS Processors Available?

Sure, there are open-source MIPS processors out there, because who doesn’t want free reign over licensing and design? You can find open-source processors that mimic MIPS architecture, allowing you to tinker without worrying about licensing fees. These projects thrive in the open-source community, giving you a chance to experiment with MIPS design without the constraints of traditional licensing. So, yes, if you’re brave enough, open-source MIPS processors are available for your hacking pleasure.

How Does MIPS Handle Power Efficiency?

You can expect MIPS processors to handle power efficiency through effective energy consumption and power management techniques. They often incorporate features like dynamic voltage and frequency scaling (DVFS), which adjusts power usage based on workload. Additionally, MIPS designs focus on reducing static power and optimizing instruction execution, helping you conserve energy without sacrificing performance. This approach makes MIPS suitable for applications where power efficiency is a priority.

Reemoon Garage Storage Cabinet with Wheels and Doors,Lockable Metal Storage Cabinet with Drawer Pegboard and Hooks for Garage Warehouse Home,Required Assembly,Black,71" H×15" D×30" W

New Upgraded:The Metal storage cabinet is designed with holes on the back and 2 side of the door....

As an affiliate, we earn on qualifying purchases.

Conclusion

Now that you understand MIPS, you see how it streamlines data processing by simplifying instructions for computers. Did you know that MIPS processors power over 50% of embedded systems in consumer electronics? This shows how essential and widespread MIPS architecture is in everyday devices. By grasping its role, you can better appreciate the technology behind your gadgets, making it easier to understand how they work seamlessly behind the scenes every day.

Dikutar Anti-Theft Bike Storage Tent with Lockable Zipper & Security Eyelets, Upgraded PU5000 Waterproof Outdoor Storage Shed for 2-3 Bikes, Bicycle Motorcycle Garden Tools Shelter (80x32x68 Inches)

【3-Layer Anti-Theft Security System】Designed for security. ① Lockable heavy-duty zipper deters casual opening. ② Rear metal security eyelets...

As an affiliate, we earn on qualifying purchases.

Sterilite 4 Shelf Cabinet, Heavy Duty and Easy to Assemble Plastic Storage Unit, Organize Bins in the Garage, Basement, Attic, Mudroom, Gray, 1-pack

Dimensions & Size: Exterior measures 25 5/8" x 18 7/8" x 69 3/8", with interior shelf dimensions of...

As an affiliate, we earn on qualifying purchases.